C'est officiel ... pour le moins pour les scientifiques.

Dans un article publié le mois passé dans "Nature" (ici), Mitchell Waldrop, éditeur de la revue et spécialiste de l'IA et des sciences de la complexité, annonce une rupture fondamentale avec la "Loi de Moore" dans la conception des microprocesseurs.

Depuis quelque cinquante ans, le développement des composants électroniques répond à un principe selon lequel leur nombre se multiplie régulièrement sur chaque puce pour chaque période temporelle. Cette loi, dite "Loi de Moore", décrivant ce développement exponentiel a subi plusieurs adaptations. Une version "Moore v1.0" est initialement publiée en 1965, prévoyant le doublement des semi-conducteurs sur les chips tous les 12 mois (x2<->1 an). La version "Moore v2.0" de 1975 dispose qu'un doublement des transistors est prévu tous les 2 ans (x2<->1,96 an). Enfin, une version plus générale "Moore v3.0", en 1992, s'accorde sur un doublement de n'importe quelle caractéristique (puissance, capacité, vitesse, fréquence…) tous les 18 mois (2<->1,5 an) avec la "feuille de route" de la « Semiconductor Industry Association » (SIA). On le voit, le développement est expansif et illimité, abordant rapidement des vitesses de développement de plus en plus faramineuses.

Pourtant, cette loi n'est plus adaptée aux générations d'objets connectés. On aborde donc une nouvelle adaptation, une version 4.0 que l'on désigne par l'expression « more than Moore ».

Les microprocesseurs de cette époque nouvelle consomment déjà moins d'énergie et intègrent de multiples capteurs. Ils contiendront bientôt d'autres éléments structuraux tels que des puces GPS, de la mémoire vive d'inspiration biologique, des puces Wi-Fi ou autres destinées à la communication des objets entre eux, des gyroscopes, accéléromètres, boussoles ou même sextants. L'époque est aux "puces hautement intégrées". Cette évolution révolutionne la loi de Moore en ce sens qu'elle apporte des propriétés bien plus importantes qu'un processeur deux fois plus rapide que le précédent pourrait le faire. Ce principe est défini dans l’« International Technology Roadmap for Semiconductors » (ITRS) de 2013. L'histoire de cette modification trouve sa source dans deux contraintes majeures.

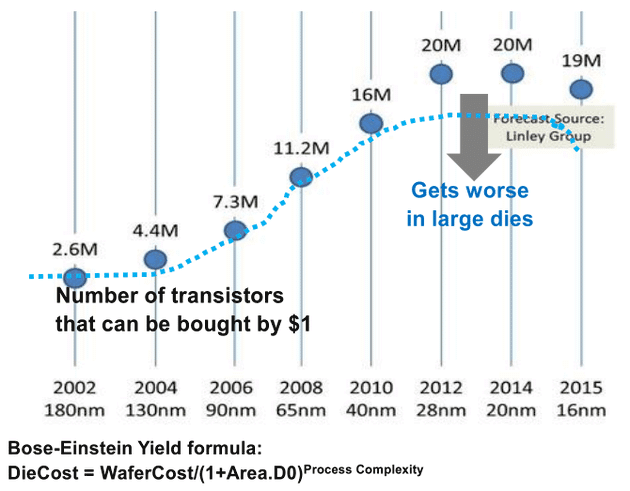

La première débute en 2000 quand il devient évident qu'une "mise à l'échelle géométrique" qui correspond à la réduction de la taille des composants pour avoir plus de transistors sur une même surface, touche à sa fin. Les modifications techniques imposées aux composants pour leur faire suivre la loi de Moore amène en 2011 à passer à la conception 3D de transistor en silicium de 22 manomètres (1nm=10^^-9m). Émergent alors plusieurs types de problèmes inhérents d'une part à la taille des transistors par rapport à la longueur d'onde qui les parcourt, et d'autre part à la chaleur produite par rapport à la fréquence du processeur. Des constructeurs se voient obligés de repousser leur conception des transistors de taille inférieure. Ainsi Intel qui prévoyait des tailles de 10nm en 2016 se voit contraint de les annoncer au mieux pour la fin 2017. Avec un tel décalage, la limite physique de 2 ou 3 manomètres ne serait pas atteinte avant 2020.

La seconde contrainte est celle de la "Loi de Rock". Celle-là postule que le coût de conception et de fabrication d'une nouvelle puce double tous les quatre ans. Or la logique de l'exponentiel impose très rapidement des coûts prohibitifs.

Pas d'autre solution que de changer de logique, et c'est ce qu'à fait l'ITRS en adoptant dès 2014 une feuille de route hors loi de Moore, dans une logique du « more than Moore » pour l'Internet des objets. Cette profonde mutation vient d'être officialisée par la publication de "Nature" (lien).

Aucun commentaire:

Enregistrer un commentaire